Назначение и структура центрального процессора

Центральный процессор

— основное устройство ЭВМ, которое наряду с обработкой данных выполняет функции управления системой: инициирование ввода-вывода, обработку системных событий, управление доступом к сновной памяти и т.п.

Организация центрального процессора (ЦП) определяется архитектурой и принципами работы ЭВМ (состав и форматы команд, представление чисел, способы адресации, общая организация машины и её основные элементы), а также технико-экономическими показателями.

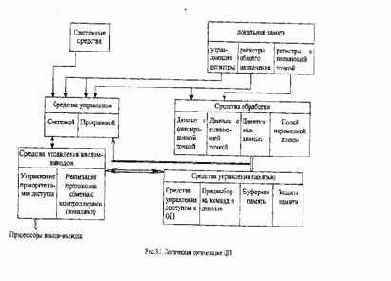

Логическую структуру ЦП представляет ряд функциональных средств (рис. 3.1): средства обработки, средства управления системой и программой, локальная память, средства управления вводом-выводом и памятью, системные средства.

Средства обработки обеспечивают выполнение операций с фиксированной и плавающей точкой, операций с десятичными данными и полями переменной длины. Локальная память состоит из регистров общего назначения и с плавающей точкой, а также управляющих регистров. К средствам управления памятью относятся средства управления доступом к ОП и предвыборкой команд, буферная память, средства защиты памяти. Средства управления вводом-выводом обеспечивают приоритетный доступ программ через контроллеры (каналы) к периферийному оборудованию. К системным средствам относятся средства службы времени: часы астрономического времени, таймер, коммутатор и т.д.

Существует обязательный (стандартный) минимальный набор функциональных средств для каждого типа центрального процессора. Он включает в себя: регистры общего назначения, средства выполнения стандартного набора операций и средства управления вычислительным процессом. Конкретная реализация ЦП может различаться составом средств, способом их реализации, техническими параметрами.

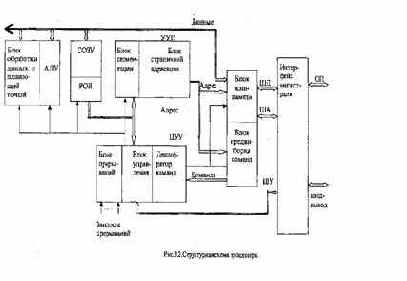

Структурно все функциональные средства разбиваются на следующие устройства (рис. 3.2): центральное устройство управления (ЦУУ), арифметико-логическое устройство (АЛУ), устройство управления памятью (УУП), сверхоперативное запоминающее устройство (СОЗУ), устройство предвыборки команд и данных (УП) и интерфейс магистрали (ИМ).

Центральное устройство управления включает дешифратор команд, блок управления и блок прерываний. Дешифратор команд дешифрирует команды, которые поступают из блока предварительной выборки (очереди команд). Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение очередной команды и переход к следующей. Блок прерываний проводит анализ запросов на прерывания, формирует сигнал прерывания работы процессора и код (вектор) запроса с наивысшим приоритетом.

Арифметико-логическое устройство выполняет все арифметические и логические операции набора команд ЭВМ. В состав устройства входят традиционные арифметико-логические блоки, специализированные аппаратные средства (блок ускоренного умножения), буферные и рабочие регистры, иногда собственный блок управления. Во многих случаях выполнение операций с плавающей точкой осуществляется в отдельном блоке (процессоре), который имеет собственные регистры данных, управления и работает параллельно с центральным процессором.

Сверхоперативное ЗУ (регистровый файл) содержит регистры общего назначения (РОН), в которых хранятся данные и адреса.

Устройство управления памятью (диспетчер памяти) предназначено для сопряжения центрального процессора и подсистемы ввода-вывода с оперативной памятью. Оно состоит из блока сегментации и блока страничной адресации, осуществляющих двухступенчатое формирование физического адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Наличие блоков сегментации и страничной адресации, их одновременное функционирование обеспечивают максимальную гибкость проектируемой системы. Сегментация полезна для организации в памяти локальных модулей и является инструментом программиста, в то время как страницы нужны системному программисту для эффективного использования физической памяти системы.

Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память (кэш-память первого уровня).

Первый осуществляет заполнение очереди команд, причем выборка из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность процессора за счет буферизации в ней часто используемых команд и данных, сокращения числа обращений к оперативной памяти.

Интерфейс магистрали реализует протоколы обмена центрального процессора с памятью, контроллерами (каналами) ввода-вывода, другими активными устройствами системы. Обмен осуществляется с помощью шин данных, адреса и управления. Состав линий управления, тактовая сетка, магистральные циклы обмена существенно отличаются у различных типов процессоров.

В современных суперскалярных процессорах используется целый ряд параллельно функционирующих исполнительных устройств (от 2 до 6 устройств). В их состав могут входить:

- несколько целочисленных устройств;

- устройство плавающей точки;

- устройство выполнения переходов;

- устройство загрузки/записи.

Устройство выполнения переходов обрабатывает команды условных переходов. Если условия перехода доступны, то решение о направлений перехода принимается немедленно, в противном случае выполнение последующих команд продолжается по предположению (спекулятивно).

Пересылки данных между кэш-памятью данных, с одной стороны, и регистрами общего назначения и регистрами плавающей точки, с другой стороны, обрабатываются устройством загрузки/записи.