Организация внутренней памяти процессора

Регистровая структура процессора была рассмотрена в разделе 3. Обращает на себя внимание ставший стандартным в современной архитектуре ЭВМ прием организации регистров общего назначения в виде сверхоперативного ЗУ с прямой адресацией

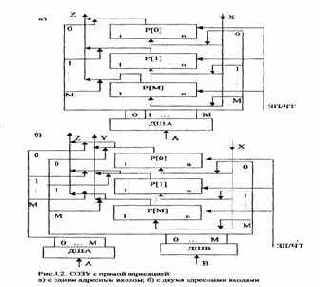

(короткие адреса регистров размещаются в команде). В машинах с коротким словом, вынуждающим прибегать к одноадресным командам, один из общих регистров выделяется в качестве аккумулятора — регистра, в котором находится один из операндов и в который помещается результат операции. Регистр аккумулятор в явном виде в команде не адресуется, используется подразумеваемая адресация. В этом случае СОЗУ с прямой адресацией (рис. 4.2, а) состоит из совокупности регистров Р[ 0" ],..., Р[ М ], связанных с входной Х и выходной Z шинами, по которым передаются n — разрядные слова. Адрес регистра, к которому производится обращение с целью записи или чтения (управляющий сигнал ЗП/ЧТ) информации, поступает по шине А. Дешифратор адреса ДША формирует управляющие сигналы 0, 1,..., М, подключающие регистр с заданным адресом к шинам СОЗУ.

При использовании двухадресных команд типа «регистр-регистр», в которых указываются адреса двух операндов, расположенных в регистрах, и результат операции помещается по одному из этих адресов, данная организация СОЗУ становится неэффективной. Это связано с тем, что за один машинный такт может быть выбрано содержимое только одного регистра. Для реализации таких команд за один такт СОЗУ строится по схеме, приведенной на

рис. 4.2, б.

СОЗУ состоит из совокупности регистров, связанных с входной шиной X и двумя выходными шинами Y, Z. Адреса регистров, к которым производится обращение с целью чтения информации, поступают по шинам А и В. Адрес регистра для записи информации поступает по входу В. Дешифраторы адресов ДША и ДШВ формируют управляющие сигналы 0, 1,... , М, подключающие два регистра к выходным шинам при чтении и один регистр к входной шине при записи.